노이즈 억제 제품 / EMI 억제 필터 / ESD 보호 장치

노이즈 억제 필터 가이드

칩 페라이트 비드에 대한 이전 논의에 이어, 이번 단원에서는 칩 3단자 커패시터를 최대한 활용하기 위해 알아야 할 사항에 대해 설명합니다.

칩 3단자 커패시터는 일반 2단자 커패시터에 비해 접지 단자의 임피던스가 낮으며, 이것이 고주파 노이즈 억제에 핵심적인 역할을 합니다. 그러나 이 기능을 활용하려면 실장 패턴 설계에 주의를 기울여야 하며 접지 측 패턴을 최대한 두껍고 짧게 설계해야 합니다. 다층 기판에 실장할 때도 비슷한 고려 사항이 적용됩니다.

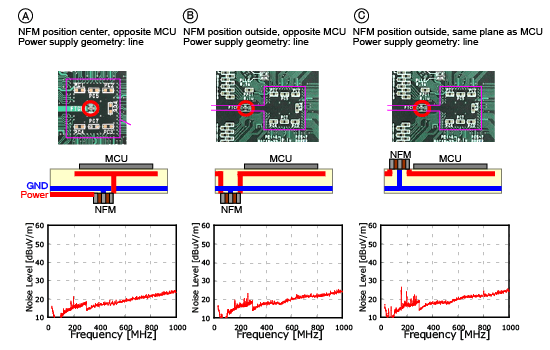

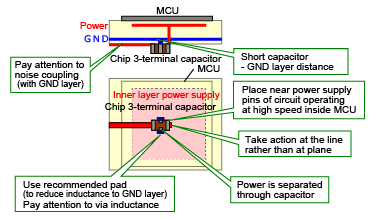

그림 1의 예는 3단자 커패시터를 다층 기판에 실장하는 방식, 특히 GND 레이어에 대한 연결 방식 변경이 잡음 억제에 미치는 영향을 보여줍니다. 이 예에서 GND 레이어는 MCU가 실장된 표면의 반대쪽 근처에 위치합니다. 3단자 커패시터가 MCU 실장 표면의 반대편에 있는 GND 레이어에 가깝게 실장된 예제 A에는 GND 레이어에 대한 짧은 연결의 예가 설명되어 있습니다. 3단자 커패시터가 MCU와 같은 평면에 실장된 예제 C는 예제 A에 비해 GND 레이어와의 거리가 더 먼 결과를 보여줍니다. 예제 A와 C의 노이즈 레벨에서 상당한 차이가 있음을 알 수 있습니다. GND 패턴을 고려할 때는 평면성만 고려하는 것이 아니라 비아의 길이도 고려해야 합니다. 그림 1의 예제 B에서는 3단자 커패시터에 대한 전원 입력과 출력이 예제 A에서 볼 수 있는 명확한 분리 없이 동일한 레이어를 통과합니다. (글로 설명하기 어려우므로 그림을 참조하세요.) 이 경우 노이즈 레벨이 예제 A보다 약간 높습니다. 이는 3단자 커패시터 입구와 출구의 비아가 너무 가깝기 때문에 비아 간의 용량 결합으로 인해 노이즈의 일부가 3단자 커패시터를 통과하지 않고 우회하는 것일 가능성이 높습니다. 이 예에서 볼 수 있듯이 3단자 커패시터에서 최상의 성능을 얻으려면 커패시터 외부의 라우팅에 주의를 기울여야 합니다. 그림 2는 칩 3단자 커패시터를 장착할 때의 핵심 사항을 보여줍니다.

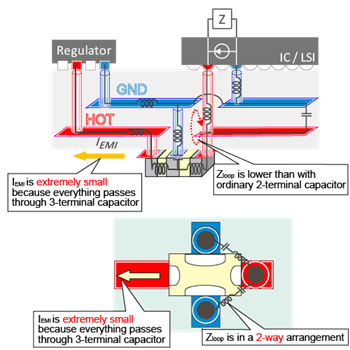

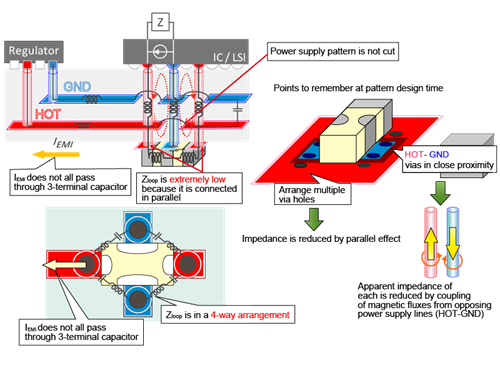

일반적으로 칩 3단자 커패시터를 사용하는 방식은 먼저 전원선과 같이 노이즈를 줄이고자 하는 선의 패턴을 잘라 커패시터를 삽입한 다음 접지 단자를 연결하는 것입니다(그림 3). 최근에는 다소 색다른 연결 방법이 제안되었습니다. 이 방법은 3단자 커패시터를 IC 전원 공급용 바이패스 커패시터로 사용하여 IC의 전압 변동을 안정화하고자 할 때 적합합니다. 이 연결 방법은 그림 4에 설명되어 있으며, 그림 3과 달리 전원 공급 패턴을 절단하지 않고 단자를 전원 공급 라인에 연결합니다. 이 연결 방식은 전원 공급 라인이 3단자 커패시터를 통과하지 않기 때문에 '비통과 연결'이라고 합니다. 전원 공급 라인과 커패시터의 연결이 병렬로 이루어지기 때문에 이 부분의 임피던스가 절반으로 줄어들고 바이패스 경로의 임피던스가 낮아지며 IC의 전압 변동이 줄어듭니다. 또한 그림과 같이 GND 측과 전원 측 비아를 서로 인접하게 배치하면 그 사이의 전류에 의해 생성된 자속이 서로 상쇄되어 이 부분의 인덕턴스가 현저히 감소하여 임피던스가 더욱 낮아집니다. 하지만 노이즈의 일부가 3단 커패시터를 거치지 않고 전원선을 통과하기 때문에 전원선을 절단한 후 3단 커패시터를 삽입하는 기존 연결 방식에 비해 외부로 빠져나가는 노이즈 감소 효과가 현저히 떨어집니다.

*이 글에 제시된 정보는 발행일 현재를 기준으로 작성되었습니다. 최신 정보와 다를 수 있습니다.