노이즈 억제 제품 / EMI 억제 필터 / ESD 보호 장치

노이즈 억제 필터 가이드

9강까지 노이즈 대책의 기본은 이미 설명해 드렸고, 그 후속으로 이번 강의에서는 노이즈 대책 부품을 사용할 때 고려해야 할 점과 문제가 발생했을 때 취해야 할 조치에 대해 설명합니다. 첫 번째 파트에서는 칩 페라이트 비드에 대해 이야기하겠습니다.

4강에서 언급했듯이 칩 페라이트 비드는 페라이트를 사용하는 인덕터의 한 유형입니다. 따라서 고전류가 흐를 때 자기 포화도에 따라 성능이 달라진다는 점을 염두에 두어야 합니다.

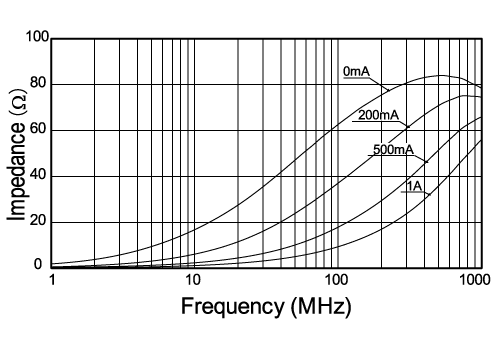

그림 1은 칩 페라이트 비드에 전류가 흐를 때 임피던스 값에서 발생하는 몇 가지 변화의 예를 보여줍니다.

그림에서 볼 수 있듯이 칩 페라이트 비드에 높은 전류가 흐르면 임피던스 값이 감소하므로, 높은 전류가 흐르는 곳에서 비드를 사용할 때 항상 기대하는 결과를 얻을 수 있는 것은 아닙니다. 이럴 때는 정격 전류에 어느 정도 여유가 있는 부품이나 초기 임피던스가 높은 부품을 선택하거나 다른 창의적인 방법을 찾아내야 합니다. 그러나 페라이트 비드에서 자기 포화는 높은 전류가 흐를 때만 발생하며, 전류가 감소하면 비드의 원래 성능이 회복됩니다. 즉, 전류가 순간적으로만 증가하는 회로에서는 문제가 발생하지 않는 경우도 있습니다(단, 그 순간의 자기 포화로 인해 문제가 발생할 수 있다는 점에 유의하세요). 실제 제품에서 수행한 평가에 따르면 페라이트 비드가 잘 작동하지 않는다고 가정할 경우 자기 포화도가 원인인 것으로 추정되지만, 구체적인 영향을 파악하기는 어렵습니다.

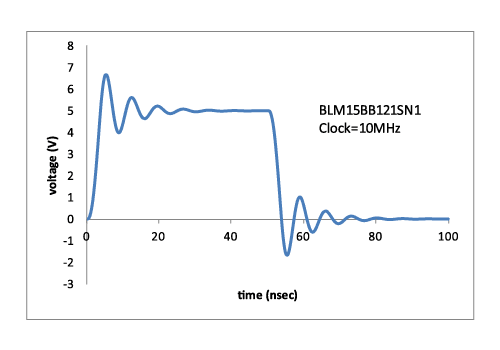

페라이트 비드를 디지털 회로에 사용할 때 파형에 오버슈트와 언더슈트가 나타나는 경우가 있습니다(그림 2 참조).

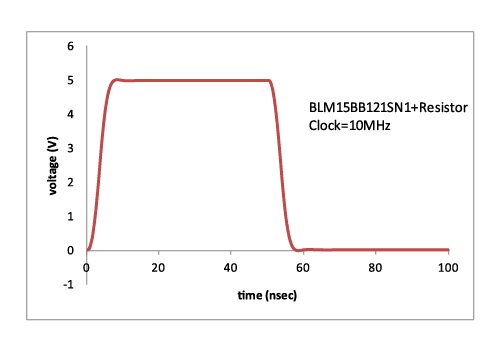

이 현상은 페라이트 비드의 인덕턴스와 회로의 다른 부분의 정적 커패시턴스(IC의 입력 커패시턴스 등)에 의해 생성되는 공진으로 인해 발생하므로 임피던스 곡선이 급격한 페라이트 비드에서 발생하는 경향이 있습니다. 이를 개선하는 한 가지 방법은 페라이트 비드에 댐핑 저항을 직렬로 삽입하는 것입니다. 댐핑 저항을 삽입하면 저항이 공진 에너지를 흡수하여 공진이 감소하고 오버슈트 및 언더슈트가 모두 감소합니다(그림 3 참조).

그러나 이러한 감쇠 저항을 사용하면 전압이 그에 상응하는 방식으로 떨어지기 때문에 신호의 파고 감소로 인해 문제가 발생하는지 여부에 주의를 기울여야 합니다. 페라이트 비드의 특성은 임피던스 곡선이 날카로울수록 내부 손실이 낮아지고 공진 발생 가능성이 높아지며, 반대로 임피던스 곡선이 완만할수록 공진 발생 가능성이 낮아지는 특징이 있습니다. 따라서 곡선이 필요 이상으로 날카로운 페라이트 비드를 사용하지 않는 것이 오버슈트 및 언더슈트를 방지하는 데 도움이 됩니다.

이번 단원에서는 페라이트 비드에 대해 알아보았고, 다음 단원에서는 칩 3단자 커패시터와 관련하여 고려해야 할 사항을 살펴볼 것입니다.

*이 글에 제시된 정보는 발행일 현재를 기준으로 작성되었습니다. 최신 정보와 다를 수 있습니다.