노이즈 억제 제품 / EMI 억제 필터 / ESD 보호 장치

노이즈 억제 필터 가이드

칩 페라이트 비드에 대한 이전 논의에 이어, 이번 단원에서는 칩 3 단자 커패시터에 대해 설명합니다.

칩 3 단자 커패시터에 대해 설명하기 전에 리드형 3 단자 커패시터에 대해 설명하면 개념을 더 쉽게 이해할 수 있습니다.

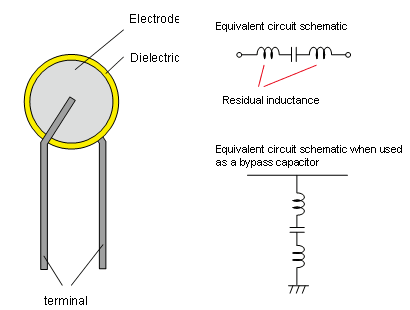

그림 1은 일반적인 리드형 세라믹 커패시터(2단자)의 구조를 보여줍니다.

리드형 세라믹 커패시터는 하나의 패널 유전체 양쪽에 전극을 코팅하고 리드 단자를 부착합니다. 이 구조에서는 리드 단자 부분에 인덕턴스(잔류 인덕턴스)가 최소화되므로 이 커패시터를 바이패스 커패시터로 사용하면 접지 단자와 사이에 인덕턴스가 발생합니다.

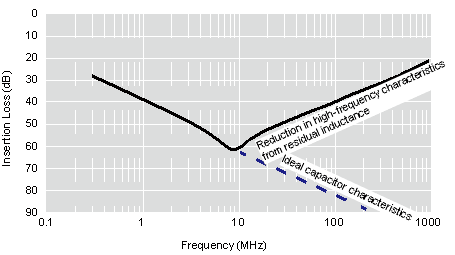

그림 2는 커패시터를 바이패스 커패시터로 사용할 때 삽입 손실 특성의 예를 보여줍니다. 이 그래프는 삽입 손실을 보여 주며, 그래프 하단으로 갈수록 노이즈 레벨이 감소합니다. 일반적으로 커패시터의 임피던스는 주파수가 증가함에 따라 비례하여 감소하므로 고주파 영역에서도 그림의 점선을 따라 삽입 손실이 계속 증가해야 합니다. 그러나 실제로 커패시터에는 앞서 언급한 잔류 인덕턴스가 있으며, 이 최소 인덕턴스가 간섭을 일으켜 실선의 V자형 삽입 손실 곡선으로 표시된 고주파수에서 성능이 저하됩니다.

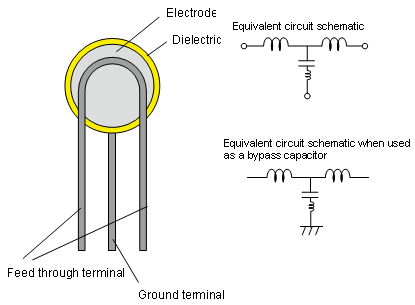

3단자 커패시터는 2단자 커패시터의 고주파 특성을 개선하기 위해 리드 단자의 모양을 변경한 세라믹 커패시터입니다. 그림 3에서 볼 수 있듯이 3단자 커패시터의 리드 단자 하나에는 두 개의 돌출부가 있습니다. 이 구성에서는 2단자 리드의 돌출부를 각각 전원 또는 신호선의 입력과 출력에 연결하고 다른 리드를 접지 단자에 연결하여 오른쪽의 등가 회로도에 표시된 연결부를 만듭니다. 이렇게 연결하면 2단자 리드 인덕턴스가 접지 측으로 들어가지 않기 때문에 접지 임피던스가 매우 작아집니다. 또한 2단자 리드의 인덕턴스가 T형 필터 인덕터와 유사하게 작동하기 때문에 노이즈를 줄이는 방향으로 작동합니다.

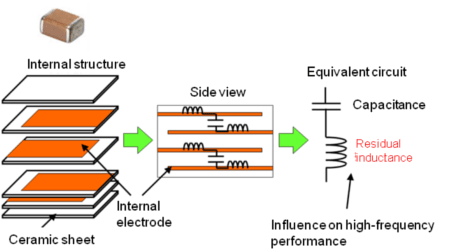

현재 가장 일반적으로 사용되는 커패시터는 칩형 다층 세라믹 커패시터입니다. 그림 4는 2단자 칩형 다층 커패시터의 구조적 개념을 보여줍니다. 유전체 시트가 플레이트 사이에 배치되고 내부 전극이 다층 또는 적층 패턴으로 전극의 돌출된 양쪽 끝에 교대로 연결됩니다. 칩 형태이기 때문에 리드가 없고 더 이상 잔류 인덕턴스가 없습니다. 그러나 내부에 최소한의 인덕턴스가 남아 있으므로 더 높은 주파수에서는 성능이 떨어집니다.

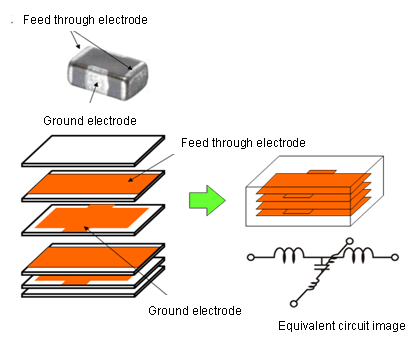

리드형 3단자 커패시터와 마찬가지로 칩 3단자 커패시터는 고주파에서의 성능 향상을 위해 전극 구조가 변경됩니다. 그림 5는 3단자 칩형 커패시터의 구조적 개념을 보여줍니다. 칩의 각 면에 접지 단자를 부착하고 유전체를 판 사이에 배치한 후 피드스루 전극과 접지 전극을 교대로 쌓아 올려 피드스루 커패시터와 같은 구조를 만듭니다. 등가 회로도에서 볼 수 있듯이 피드 스루 전극의 인덕턴스는 3단 리드 커패시터의 조건과 유사하게 T형 필터 인덕터처럼 작동하므로 잔류 인덕턴스의 영향이 적습니다. 접지 측과의 거리가 짧아 이 부분의 인덕턴스가 최소화됩니다. 또한 접지 측이 양쪽 끝에 연결되어 직렬로 연결되므로 인덕턴스가 절반으로 줄어듭니다.

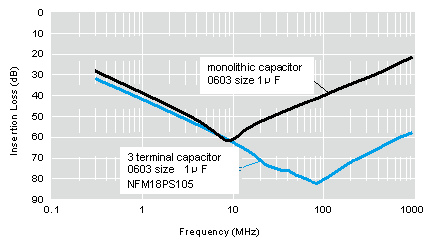

그림 6은 칩 3단자 커패시터와 2단자 칩형 다층 커패시터의 삽입 손실 특성을 비교한 것입니다. 각 유형에서 커패시턴스는 동일하므로 저주파 영역에서 유사한 특성을 보입니다. 그러나 2단자 커패시터는 10MHz를 초과하면서 성능이 떨어지기 시작하고, 3단자 커패시터는 100MHz 부근까지 성능을 유지합니다. 3단자 칩형 커패시터는 고주파 영역에 도달할 때까지 성능이 저하되지 않기 때문에 고주파까지 노이즈 억제가 필요한 애플리케이션에 유용합니다.

그림 5에서 볼 수 있듯이 칩 3단자 커패시터는 단자가 3개라고 하지만 실제로는 4개입니다. 단자가 4개이면 접지 측의 임피던스를 더 줄일 수 있지만, 칩으로 만들어도 전기적으로 모든 단자의 전위가 같고 원래 리드형 3단자 커패시터는 단자가 3개였기 때문에 여전히 '3단자' 커패시터라고 부릅니다.

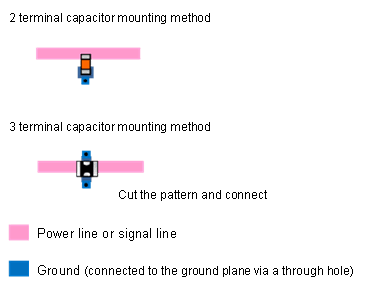

칩 3 단자 커패시터에는 피드스루 단자와 접지 단자가 있기 때문에 장착 방법이 일반 2 단자 커패시터와 다릅니다. 그림 7은 장착 방법을 보여줍니다.

3단자 칩형 커패시터를 바이패스 커패시터로 장착하는 경우 신호 또는 전원 패턴을 차단하고 그 사이에 피드스루 전극을 연결하고 접지 단자에 접지 패턴을 준비하여 연결합니다. 접지 패턴은 최소한의 임피던스를 유지하기 위해 안정적인 접지면에 가능한 한 짧게 연결해야 합니다. 양면 보드 또는 다층 보드를 사용하는 경우 스루홀을 통해 접지면에 연결하는 것이 좋습니다.

*이 글에 제시된 정보는 발행일 현재를 기준으로 작성되었습니다. 최신 정보와 다를 수 있습니다.