콘덴서

커패시터 가이드

이 기술 칼럼에서는 커패시터의 기본에 대해 설명합니다.

이 파트에서 다루는 주제는 다층 세라믹 커패시터의 구조와 이러한 커패시터 생산에 관련된 프로세스에 대해 설명합니다.

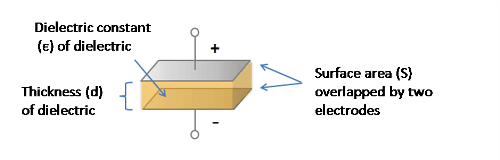

커패시터가 전하를 저장하는 데 사용하는 가장 기본적인 구조는 아래 그림 1과 같이 유전체로 분리된 한 쌍의 전극으로 구성됩니다.

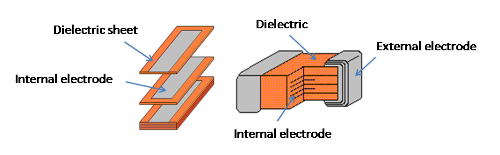

커패시터의 성능을 표현하는 데 사용되는 지표 중 하나는 얼마나 많은 전하를 저장할 수 있는지입니다. 다층 세라믹 커패시터의 경우 그림 1과 같은 구조를 층층이 반복함으로써 저장할 수 있는 전하의 양이 증가합니다. 그림 2는 그 결과의 기본 구조를 보여줍니다.

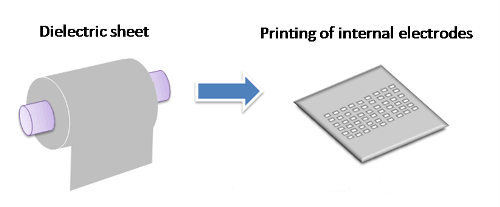

유전체의 원재료가 완성되면 다양한 용매 및 기타 물질과 혼합하고 분쇄하여 슬러리 형태의 페이스트를 만듭니다. 이 페이스트는 얇은 시트로 형성되고 아래에 설명된 8가지 제조 공정을 거친 후 다층 세라믹 커패시터 칩으로 완성됩니다.

롤 형태로 만들어진 유전체 시트는 내부 전극이 될 금속 페이스트로 코팅됩니다. 최근에는 다층 세라믹 커패시터의 내부 전극에 니켈이 주요 금속으로 사용되고 있으며, 이러한 커패시터의 경우 유전체 시트에 니켈 페이스트가 코팅되어 있습니다.

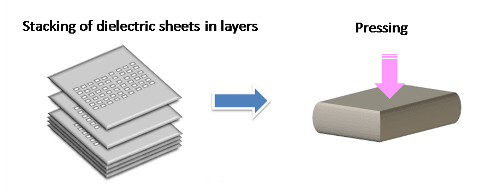

유전체 시트에 내부 전극 페이스트를 코팅한 후, 시트는 서로 겹겹이 쌓입니다.

유전체 시트의 적층된 층에 압력을 가하여 압착하고 형성합니다. 일반적으로 지금까지의 공정은 재료에 이물질이 들어가지 않도록 클린룸에서 진행됩니다.

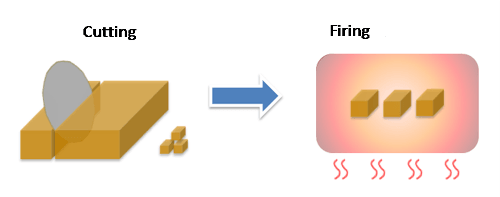

적층된 유전체 블록은 1.0mm × 0.5mm, 1.6mm × 0.8mm 또는 기타 특정 칩 크기로 절단됩니다.

절단된 칩은 섭씨 1000~1300도 범위의 온도에서 소성됩니다. 그 결과 세라믹과 내부 전극이 하나의 통합된 전체로 만들어집니다.

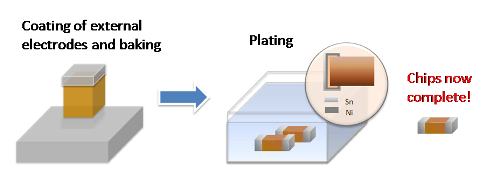

소성된 칩의 양쪽 끝은 외부 전극이 될 금속 페이스트로 코팅됩니다. 내부 전극에 니켈을 사용하는 경우 구리 페이스트를 바르고 약 섭씨 800도의 온도에서 칩을 구워냅니다.

외부 전극을 구운 후 니켈 한 층과 주석 한 층을 표면에 도금합니다. 일반적으로 전해 도금이 사용됩니다: 니켈 도금은 신뢰성 향상을 위한 것이고 주석 도금은 솔더 장착을 용이하게 하기 위한 것입니다. 이 과정을 거치면 칩이 완성됩니다.

마지막으로 완성된 칩을 검사하여 규정된 전기적 특성을 갖췄는지 확인한 후 테이핑하거나 다른 형태로 포장하여 배송합니다.

최근 다층 세라믹 커패시터는 점점 더 작아지고 정전 용량이 증가하면서 유전체 층이 더 얇아지고 층을 쌓는 정밀도가 향상되는 등 제조 공정이 개선되고 있습니다.

담당자 무라타 제조 주식회사 Y.G

이 문서에 제시된 정보는 발행일 기준으로 최신 정보입니다. 최신 정보와 다를 수 있습니다.